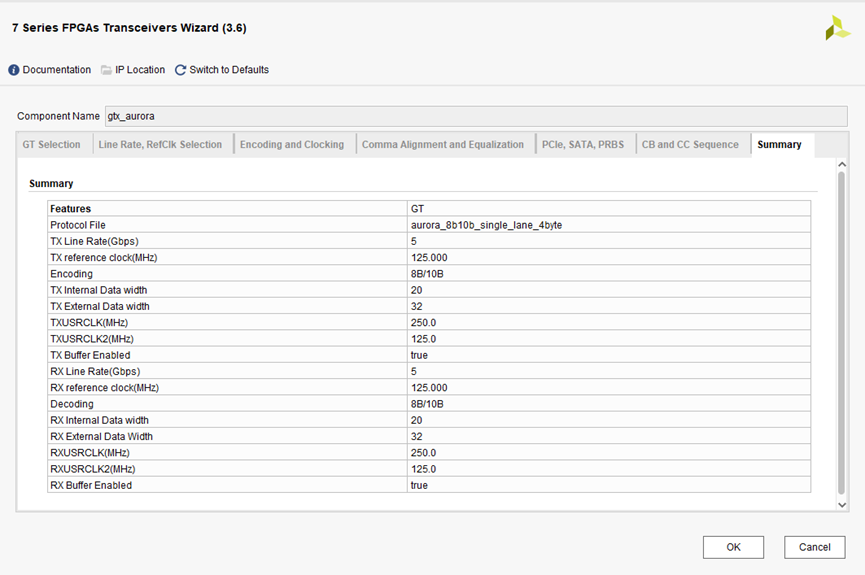

:内部数据宽度设置为20(16bit数据利用8b10b编码为20bits),两个内部数据拼接为1个32bit外部数据,编码方式采用8b10b编码,这种编码方式最主要的目的是保持 直流平衡,根据特定的编码表实现数据传输过程中0和1的数量基本一致,减少连续0或1的情况。DRP/System Clock是动态重配置/系统工作时钟,通过DPR可以根据所配置线速率和协议实时调整收发器参数。DRP时钟频率设置为100MHz,可以通过外部PLL产生,利用DRP时钟初始化一些GTX或者参数;

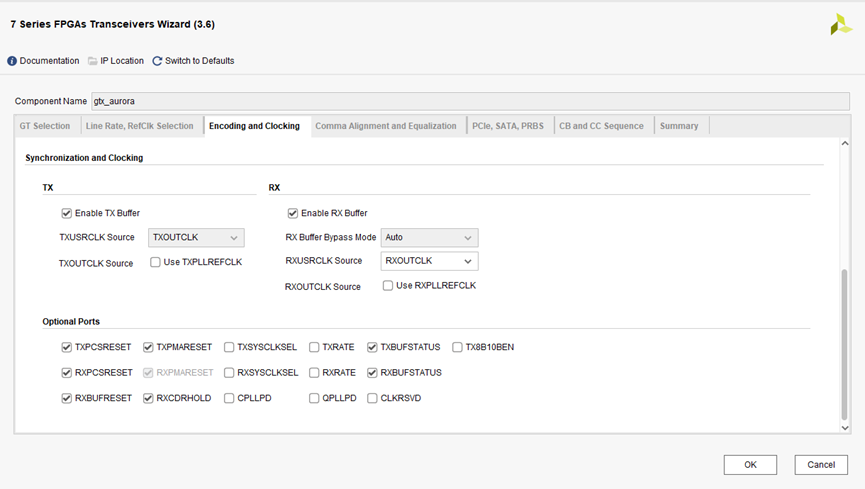

Synchronization and Clocking:TXUSERCLK,和 RXUSERCLK 时钟的选择一般TXUSERCLK可以直接选择TXOUTCLK作为用户时钟,而RXUSERCLK可以选择TXOUTCLK也可以选择RXUSERCLK,还可以选择RXPLLREFCLK作为用户时钟。这里就涉及到一个同步的概念,如果时钟不一致必须设置TX和RX的 BUFFER,默认都是设置的。另外输入TX的发送时钟和RX的恢复时钟差异交大,可能会导致RX BUFFER的溢出或者读空,而导致数据出错。比较好的解决办法就是设置RXUSERCLK为RXOUTCLK,就是利用恢复时钟作为用户时钟,这样就很好的解决了同步的问题了。

Comma Value:设置K码为K28.5,K码用于修正数据对齐,选项保持默认配置即可;

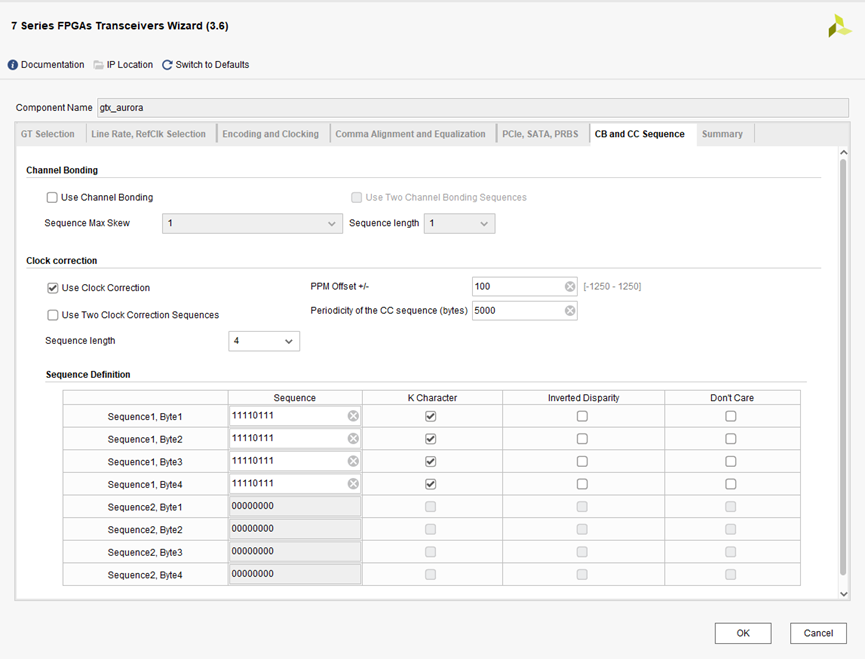

Clock correction:选择支持时钟校准,设置每5000个字节发送一组CC Seq,因为从数据流中恢复出来的时钟和本地产生的FIFO读侧的时钟的频率不可能完全一致,所以才要进行CC处理。这个周期是根据发送侧和接收侧的时钟差算出来,然后再根据实际调试结果进行一定的修正。

由于开发板的SFP屏蔽笼的tx_disable引脚都默认接了上拉电阻。要使收发回环测试可以正常进行,必须要将tx_disable引脚拉低。因此,在example design的顶层模块,添加2个sfp_tx_disable引脚,且均置为0即可;

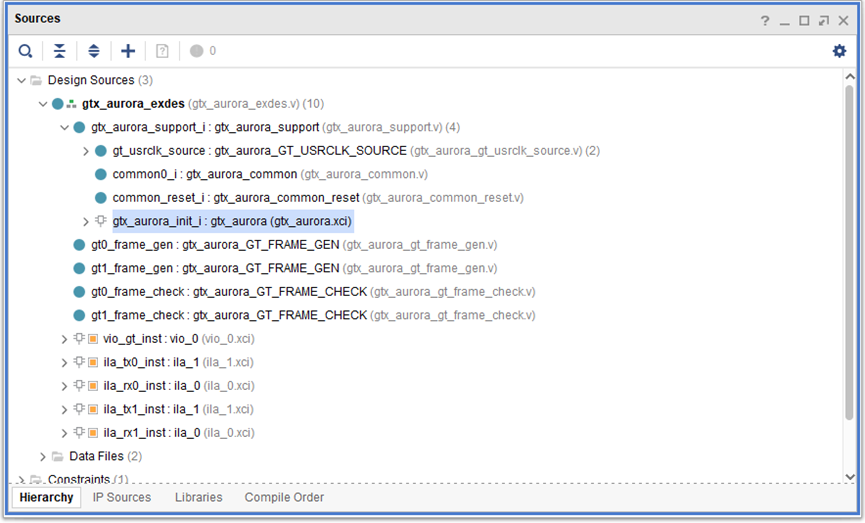

将drp_clk直接连入sysclk,官方例程这个时钟是引脚进来的加了bufg,该工程用PLL产生;

接下来我们将在硬件上实现回环传输测试数据的功能,首先我们需要从外部给出一个自由时钟,hb_gtwiz_reset_all_in复信号是高电平有效,用户直接拉低即可。由于开发板的SFP屏蔽笼的tx_disable引脚都默认接了上拉电阻。要使收发回环测试可以正常进行,必须要将tx_disable引脚拉低;

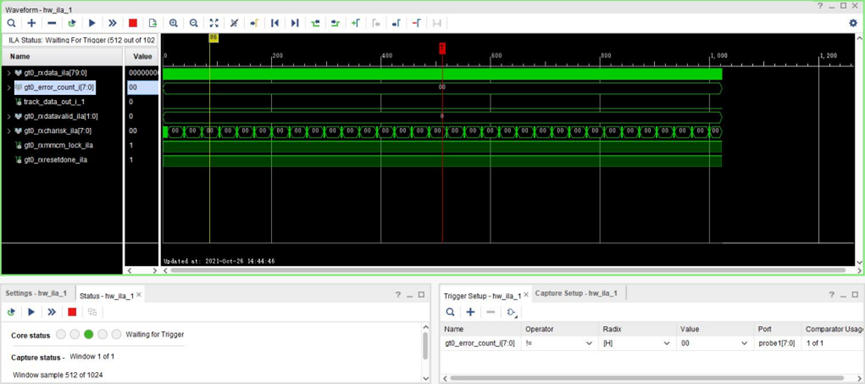

本工程实现功能为光纤信号8b10b回环传输,FPGA板上测试结果如下图所示,可以看到gt0_error_count_i信号保持为0,也就是说8b10b光通信传输正常。

、PTN/OTN等热门技术的开发中,可以预计其成熟度和性价比将进一步改善。 随着“宽带中国”上升到国家战略,中国得天独厚的优势将使

IP模块时,在用modelsim功能仿真时,一切正常。 但是直接使用了例化后的example,并将Tx和Rx形成了回路下到

v8.3,两个FIFO(Tx和Rx)和sram模块。我使用ISim模拟了总应用程序。我得到了所需的结果。现在,我的疑问

建立仅传输(流媒体)。现在使用Vivado 2014.4进行模拟阶段。我知道GTXE2_COMMON原语需要在设计中使用以包含一个QUAD PLL

引脚上提供外部时钟源(ML505-virtex5)的参考信号。 clcok源工作正常。但在我的设计中PLL没有被锁定。这是否意味着我没有得到时钟?谢谢,Abinaya

基本原理在正常照明前提下,将信息调制到LED灯发出的可见光中,接收端利用光电检测器(PD)将可见光并转换为电信号,并从中解调出相应的调制信息。基于可见

基本原理在正常照明前提下,将信息调制到LED灯发出的可见光中,接收端利用光电检测器(PD)将可见光并转换为电信号,并从中解调出相应的调制信息。基于可见

是什么意思,它的应用有哪些? /

AD8229,pdf datasheet (Instrumentation Amplifier)

【Longan Pi 3H 开发板试用连载体验】给ChatGPT装上眼睛,并且还可以语音对线,系统基础配置

【Longan Pi 3H 开发板试用连载体验】给ChatGPT装上眼睛,还可以语音对线 阅读

400-677-3888